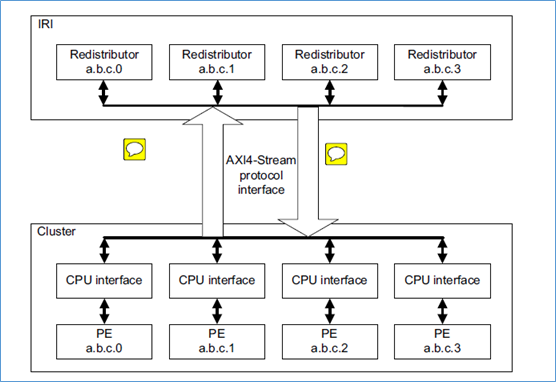

gic stream协议,是基于AXI-stream协议。用于gic的IRI组件(interrupt routing infrastructure),和cpu interface之间,传输信息。

distributor,redistributor和ITS,统称为IRI组件。

gic stream协议,包含以下2个接口:

-

下行AXI-stream接口:用于IRI向cpu interface传递信息,连接

-

上行AXI-stream接口:用于cpu interface向IRI传递信息

如下图所示:

Contents

一、接口信号

接口信号,包含下行接口信号,和上行接口信号。无论是上行还是下行,都是基于AXI-stream协议,通过data信号,来传输数据,data信号的位宽,也是固定的,为16bit。

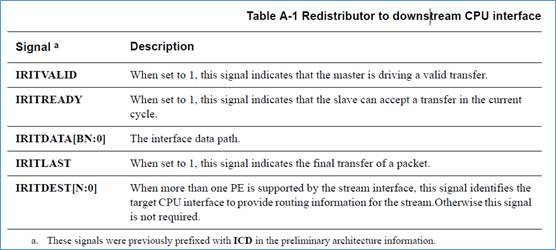

1、下行接口信号

下行接口信号如下表所示,接口协议是基于AXI-stream协议。

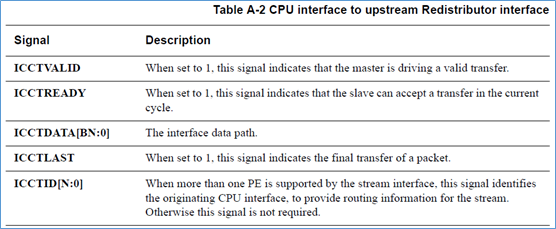

2、上行接口信号

上行接口信号如下表所示,接口协议是基于AXI-stream协议。

二、包

IRI与cpu interface通过gic stream协议传输信息,传输的信息,是以包为单位。包,分为两类包:

-

命令包,分为redistributor命令包,cpu interface命令包

-

响应包,分为redistributor响应包,cpu interface响应包

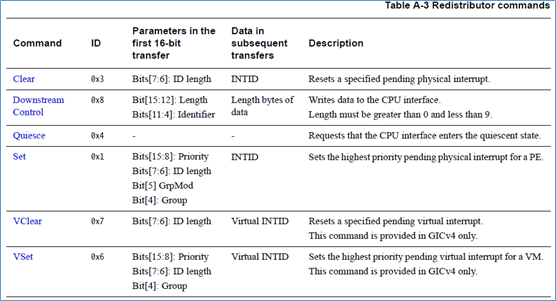

AXI-stream协议,每次传输2个字节,多次传输,组成一个包。不同的包,大小不是一样的,比如有的是16个字节,有的是8个字节。包传输的第一个16bit数据,表示包的类型。

如果一个组件,发送命令包,那么另一个,需要回应响应包。

1、redistributor命令包

下图是下行redistributor命令包。

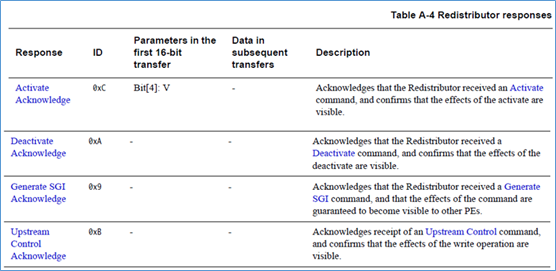

2、redistributor响应包

下图是上行redistributor响应包。

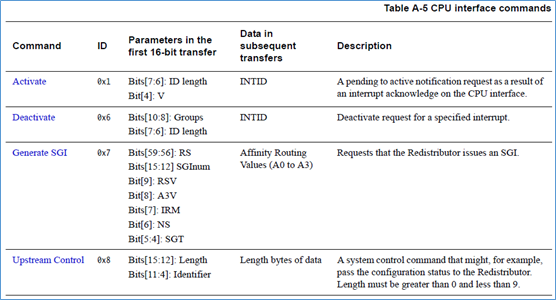

3、cpu interface命令包

下图是cpu interface命令包。

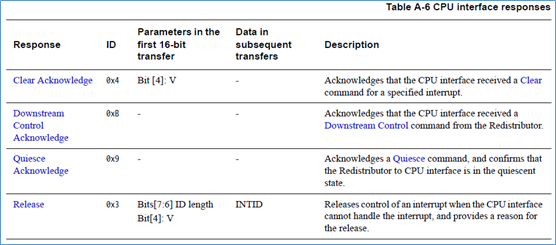

4、cpu interface响应包

下图是cpu interface响应包。

5、例子

以下是cpu interface的activate命令包,格式如下:

这个activate命令,由cpu interface发送给IRI,表示认可中断,中断号,由包中的INTID字域来表示。

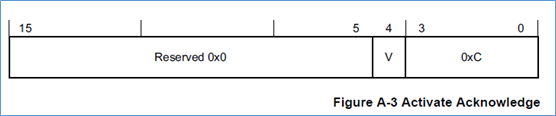

IRI在收到cpu interface的activate命令后,会回发activate acknowledge响应包。表示,IRI接收到cpu interface的activate命令。

其格式,如下所示:

包在传输的过程中,先发第一个数据的低16bit数据,再发第一个数据的高16bit数据,如果还有下一个数据,按照上述流程发送。所以,命令的类型,是最先发送的。

三、包传输流程

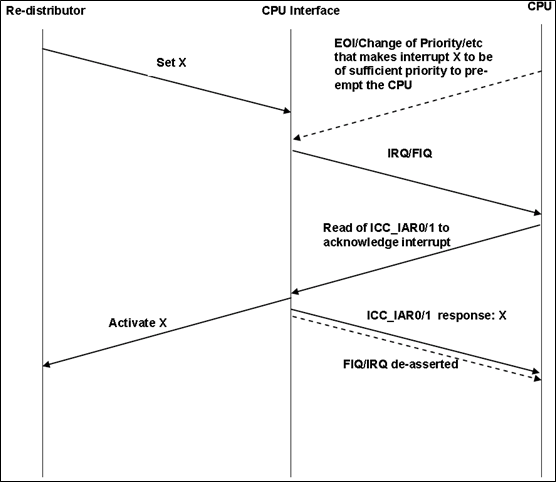

1、中断发送

如下图,redistributor,要发送一个中断给cpu。包的传输的流程,如下:

-

redistributor给cpu interface发送set命令,发送中断X请求,cpu interface接收到该命令后,如果该中断X符合当前优先级要求,CPU interface通过IRQ/FIQ给cpu发送中断。

-

CPU响应CPU interface发送的中断,于是去读取ICC_IAR寄存器,表示认可该中断,得到中断号。之后cpu interface给redistributor发送activate响应。然后把IRQ/FIQ给取消掉。

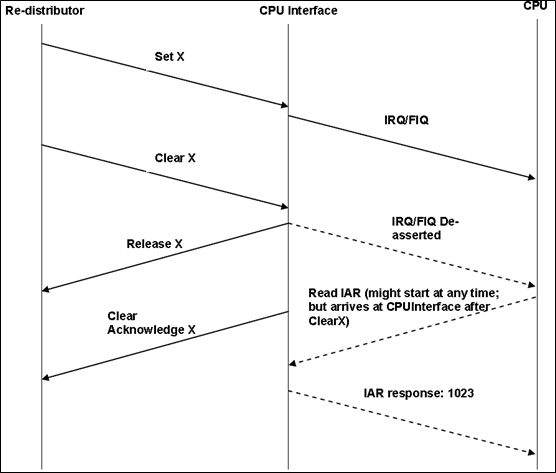

2、中断取消

CPU在读取ICC_IAR寄存器前,redistributor取消中断。包的传输流程,如下:

-

redistributor给cpu interface发送set命令,cpu interface接收到该命令后,通过IRQ/FIQ给cpu发送中断。

-

redistributor给cpu interface发送clear命令,清除该中断,cpu interface将IRQ/FIQ拉低。然后回release响应。

-

cpu interface给redistributor,回clear acknowledge响应。

-

如果此时,cpu读取IAR寄存器,CPU会获取到一个假的中断号。

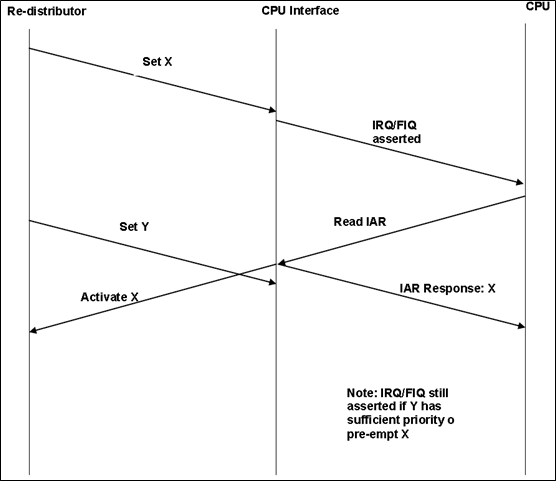

3、两个中断

redistributor给cpu interface发送两个中断。包的传输流程,如下图所示:

-

redistributor,首先发送set x命令,发送中断x。cpu interface接收该命令,将IRQ/FIQ拉高,向CPU发送中断请求。

-

cpu读取ICC_IAR寄存器,认可该中断x,开始处理该中断x。cpu interface给redistributor回activate x响应。

-

之后,redistributor给CPU interface发送set y命令,发送中断y。在cpu interface中,如果y的优先级符合要求,那么IRQ/FIQ会一直有效。等待CPU处理。

4、中断抢占

redistributor给cpu interface发送2个中断,第二个中断抢占第一个中断。包的流程如下:

-

redistributor,首先发送set x命令,发送中断x。cpu interface接收该命令,将IRQ/FIQ拉高,向CPU发送中断请求。

-

在cpu读取ICC_IAR寄存器之前,redistributor,又给cpu interface发送了set y命令,发送中断y。并且y的优先级比x高。

-

cpu interface给redistributor回release x响应,表示cpu interface暂时不处理中断x,中断x,将来重新发送。

-

CPU读取ICC_IAR寄存器,认可中断y。cpu interface给redistributor回activate y响应。

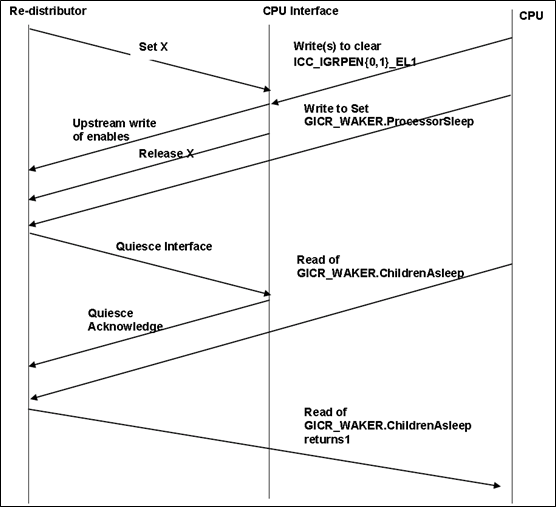

5、电源断电

gic给CPU发送中断,使CPU断电。

这个,就比较复杂了。就不解析了。

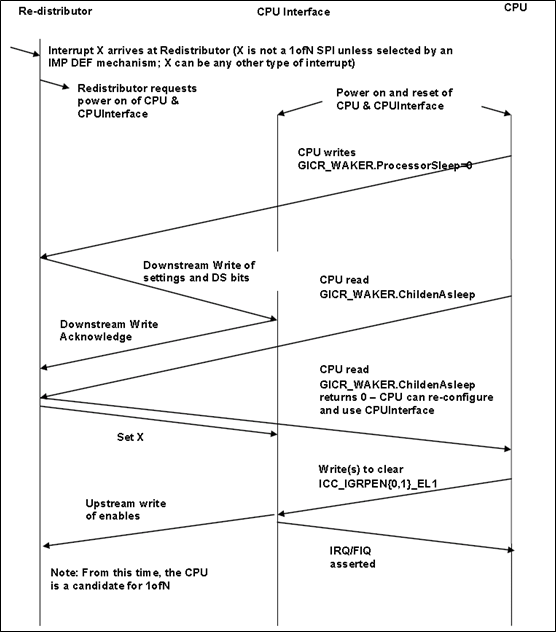

6、电源上电

redistributor,请求将CPU和cpu interface上电。

这个也比较复杂,这里不解析。

四、总结

gicv3中,IRI与cpu interface之间,是通过包,来传输信息。传输的接口协议,使用AXI-stream。通过包的各种组合,来实现gic的中断操作与中断管理。

之后,会介绍gicv3中,引入的一种新的中断类型,消息中断。

作者您好,请问上面数据包的部分是参考的哪个PDF文档,谢谢!