之前说明了软件控制硬件的原理,本质上就是控制寄存器。但是软件也只能控制一个寄存器,那如果要控制多个寄存器了,那又该怎么办呢?这个时候,你就得了解片上总线互联技术了,为什么是片上了,因为这些都是在芯片里面实现的,所以就叫片上了。

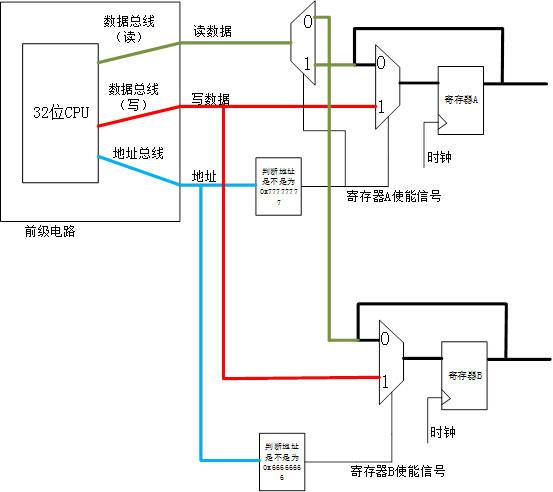

下面假设有两个寄存器,软件要对这两个寄存器进行操作。那原理图就应该是下面这样的:

两个寄存器,就会有两个地址,这里设定A地址是0x77777777,寄存器B地址是0x66666666。因为只有两个寄存器,不是读寄存器A的值就是读寄存器B的值,所以使用寄存器A的使能信号判断读的数据是哪一个寄存器的值就可以了。

以上就是两个寄存器的情况,那如果现在要再加一个寄存器了,那就给这个寄存器设定一个地址,然后加一个判断地址是否使能的电路,再修改上面的读数据的部分。这样的话,当增加的寄存器多了,那要改的地方就多了,不利于扩展。

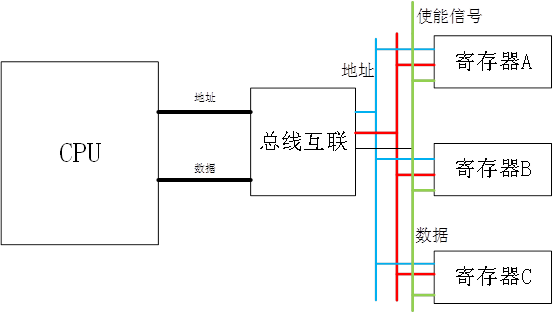

所以出现总线互联模块来解决上面的问题,CPU发出的地址和数据不直接连接到寄存器上,而是先连接到总线互联模块,再由总线互联模块决定地址和数据以及产生的使能连接到哪个寄存器上。示意图为以下:

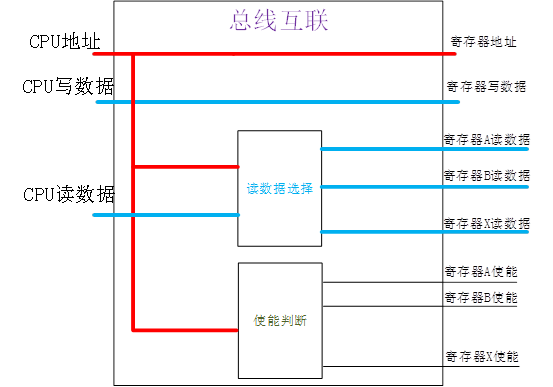

将使能信号判断,放在了总线互联中。总线互联结构也比较简单,结构如下图所示:

有了上面总线互联,当要增加外部的寄存器的时候,就简单了,直接将寄存器的地址线接到总线互联的寄存器地址上,寄存器的写数据接到总线互联的寄存器写数据上,如果需要从寄存器读取数据,就将寄存器的读数据接到总线互联的寄存器X读数据上,再把总线互联的寄存器X使能接到寄存器的使能上。

这样,就简化了外部寄存器与CPU通信接口的设计,只要外部寄存器按照总线互联的接口设计,就能够直接挂接在总线互联上,这个时候只需简单更改下总线互联的电路,CPU就可以对新加入的寄存器进行操作了。

通过片上互联总线,只要地址允许,就可以挂接无限的寄存器供CPU进行操作。但是,新的问题又来了,我们知道CPU是在时钟的控制下,一个时钟一个时钟的执行指令,也就是CPU对寄存器的操作只能是在一个时钟内,因为在下一个时钟,执行新的指令,CPU发出的数据和地址就可能变化了,那问题来了,如果CPU对寄存器的操作在一个时钟内操作完成不了了,那又该怎么办了,了解CPU原理的都知道,这个时候,就要让CPU暂停流水线,一直执行操作寄存器的指令,直到操作寄存器完成后,再开启流水线,执行之后的指令,但是CPU怎么知道寄存器有没有操作完成了?这个时候,就要引入总线协议了。

CPU对寄存器操作,不只要有总线,还要有总线协议,这样才能准确无误的对寄存器进行操作。