在cpu的验证中,需要进行dvfs的验证,也就是在仿真过程中,时钟周期不再是固定的周期,而且时钟也不是一直有效。

在这种情况下,对于时钟的生成,就不能用简单的时钟生成代码来实现:

reg clk; initial begin clk = 0; forever #HALF_PERIOD clk = ~clk; end

此时要用稍微复杂的时钟代码生成:

module test(); reg clk; //dvfs output clk int half_period; //clk half period int dvfs_period; //dvfs_disable half period reg dvfs_disable; initial begin dvfs_disable = 1; clk = 0; while(1) begin fork // generate clk begin half_period = $urandom_range(5,30); while(1) begin #half_period clk = 1; #half_period clk = 0; if ( !dvfs_disable ) break; end end // generate dvfs_disable begin dvfs_period = $urandom_range(300,600); #dvfs_period dvfs_disable=0; #dvfs_period dvfs_disable=1; end join end end endmodule

在一个while1无限循环中,有一个fork join代码块,里面包含两部分并行执行代码,一部分是生成时钟,另外一个生成dvfs_disable。

时钟在产生之前,首先使用随机函数,得到随机的半周期值。时钟在产生完一个周期后,要判断此时是否dvfs_disable为0,为0,表示时钟要关掉,此时就退出时钟产生代码块。于是时钟就停留在低电平。

而dvfs_disable,根据随机的周期值,而进行翻转。为0,表示时钟关闭,为1,表示时钟不关闭。

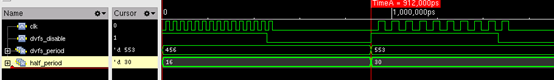

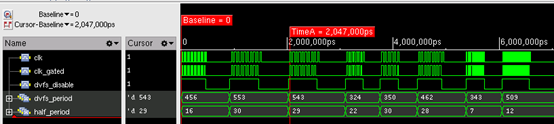

仿真的波形如下所示:

当dfvs_disable为高,表示时钟有输出,此时clk正常输出。当dvfs_disable为低,表示时钟关闭,此时clk输出为0。

第一次输出的时钟半周期为16,第二次输出的时钟半周期为30。符合dvfs的要求。