下面,简单介绍下,该软件的一些功能。

Contents

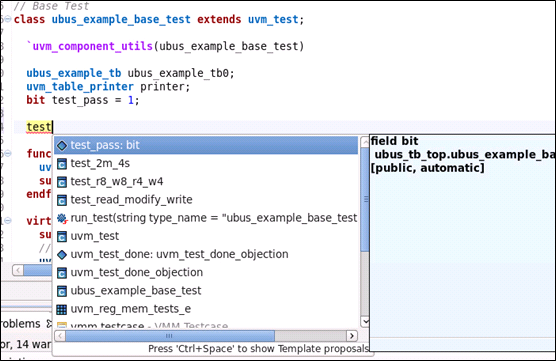

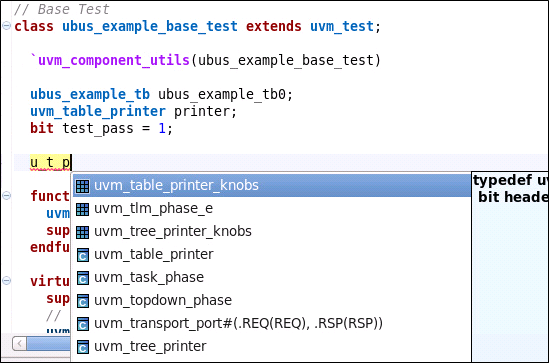

一、自动补全

输入一部分,按 ctrl + 空格,就会弹出对话框,进行选择,要自动补全的内容。

DVT还支持,缩写补全,比如上面的 uvm_table_printer ,可以输入 u_t_p,然后按 ctrl + 空格,就会自动补全成uvm_table_printer。

二、显示类的类型层次关系

对于一个类,可以查看该类的类型层次关系。

对类名,右键 Show->Type Hierarchy,或者F4。

可以显示类的类别层次关系。可以看出,该类,ubus_example_base_test类继承uvm_test,uvm_test继承uvm_component,最终从uvm_void继承而来,而ubus_example_base_test又有3个子类,分别是test_2m_4s,test_r8_w8_r4_w4,test_read_modify_write这3个类。

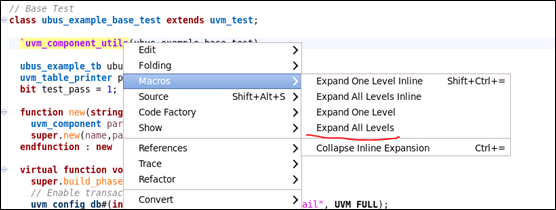

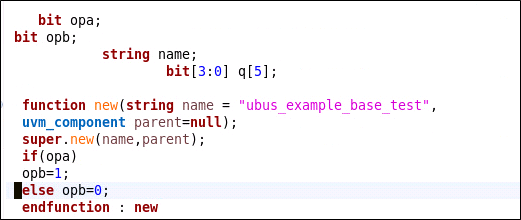

三、宏展开

这个功能,是我让我感觉到有亮点的一个功能。对于v,sv写的宏,不论是VCS工具,还是IRUN工具等,都没法将宏进行展开,让我们能清晰的看清楚,宏被替换后的代码是怎么的,但是DVT工具,提供了这个功能。

比如在UVM中,我们会使用 `uvm_component_utils 宏来进行类的注册。但是这个宏展开后,是什么样,就不知道了。

对宏名,右键,Macros->Expand All Levels。

就可以看到展开之后的宏的代码,并且宏参数,已经进行了替换。从这里,也可以清晰的看出,type_id这个东西,是类中一个类类型。

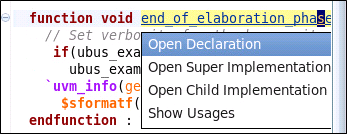

四、查看申明,文件跳转

对一个函数,可以查看该函数的申明,对于include的文件,可以查看源文件。对需要查看的东西,鼠标放在之上,然后按住ctrl键,会弹出对话框,进行选择,即可实现跳转。

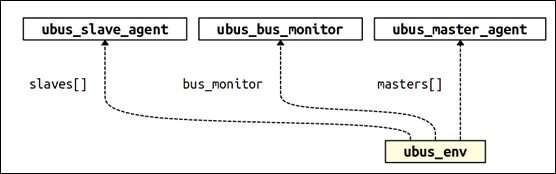

五、显示UVM结构

对于UVM搭建的环境,我们一般是在环境中,使用print_topology函数,打印出UVM的结构。但是在DVT中,可以直接,查看UVM的结构。

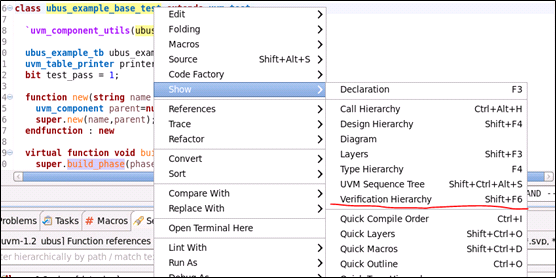

对顶层的test,右键,Show->Verification Hierarchy。

在右边的Verification Hierarchy,就会显示当ubus_example_base_test作为UVM的顶层时,UVM的结构。

六、显示类的UML图

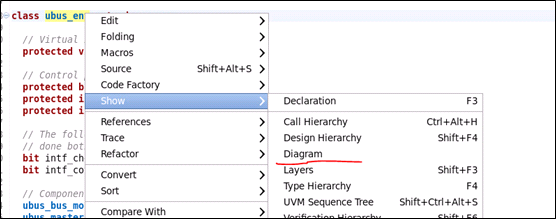

对类名,右键 Show->Diagram。

可以得到该类的UML图。

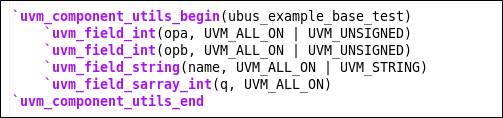

七、自动生成UVM_FIELD

对于如下的变量,想要使用field automation机制。

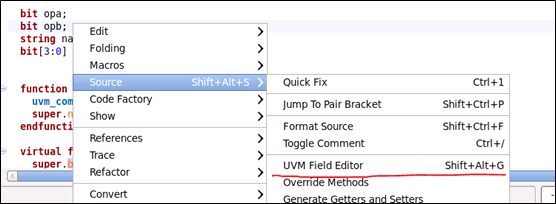

代码区域,右键,Source->UVM Field Editor。

弹出对话框,左边选择需要field automation的变量,右边,选择参数。

点击OK,就会生成代码。

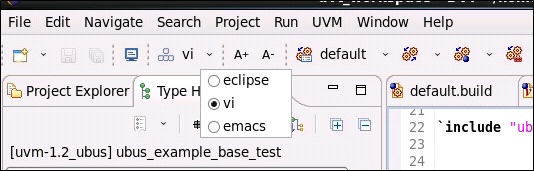

八、编辑器选择

对于在linux下工作,一般喜欢用vi,或者emacs,DVT功能,也支持这些编辑器。

在右上角,4个方框组成的图形,边上有下拉菜单,可以选择使用哪一种编辑器。

九、代码格式调整

对于以下这段代码,格式不友好。

代码区,右键,Source->Format Source。对代码格式进行调整。

调整后,格式变得友好。

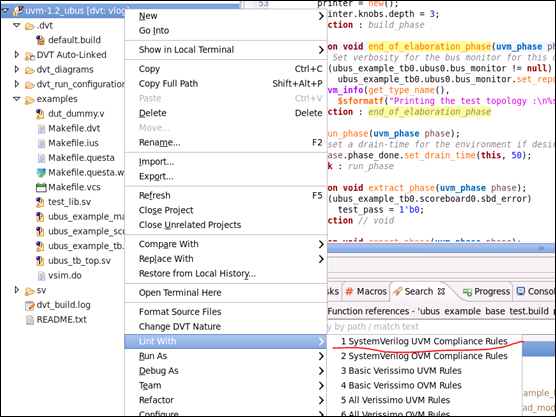

十、lint功能

可以对工程,进行line操作,进行统计。

工程右键,Lint with->SystemVerilog UVM Compliance Rules。

弹出对话框,根据需要进行选择。

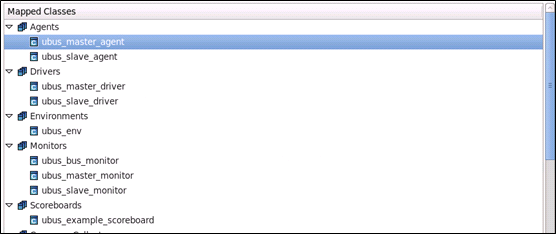

如对于Architecture,根据分类,显示各个类。

十一、工程build

当对代码进行修改完毕后,必须重新进行一次build。

工程右键,Project->Rebuild。

该软件的功能,还有很多,这就需要大家在使用的时候,多尝试,多摸索了。